## Traineeships in Advanced Computing for High Energy Physics (TAC-HEP)

GPU & FPGA module training: Part-2

**Week-6**: Project: Re-designing RCT

Lecture-12: April 26th 2023

#### So Far...

- FPGA and its architecture

- Registor/Flip-Flops, LUTs/Logic Cells, DSP, BRAMs

- Clock Frequency, Latency

- Extracting control logic & Implementing I/O ports

- Parallelism in FPGA

- Scheduling, Pipelining, DataFlow

- Vivado HLS

- Introduction, Setup, Hands-on for GUI/CLI, Introduction to Pragmas

- Different Pragmas and their effects on performance

- Practices to follow while writing HLS code do's & don'ts

- LHC and CMS Experiment: Level-1 Trigger System

#### **Today:**

More on Project:

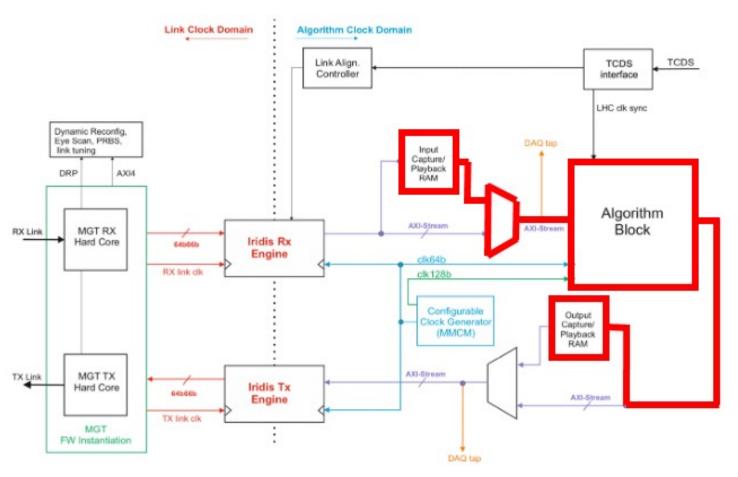

#### APx Firmware Shell

- Encoding/Decoding

- Current Protocol

- 67b65b

- 64b is data

- 2 or 3b are control signals (Start, resets, debugging errors, etc ...)

## Regional Calorimeter Trigger

$12.5 \mu s$

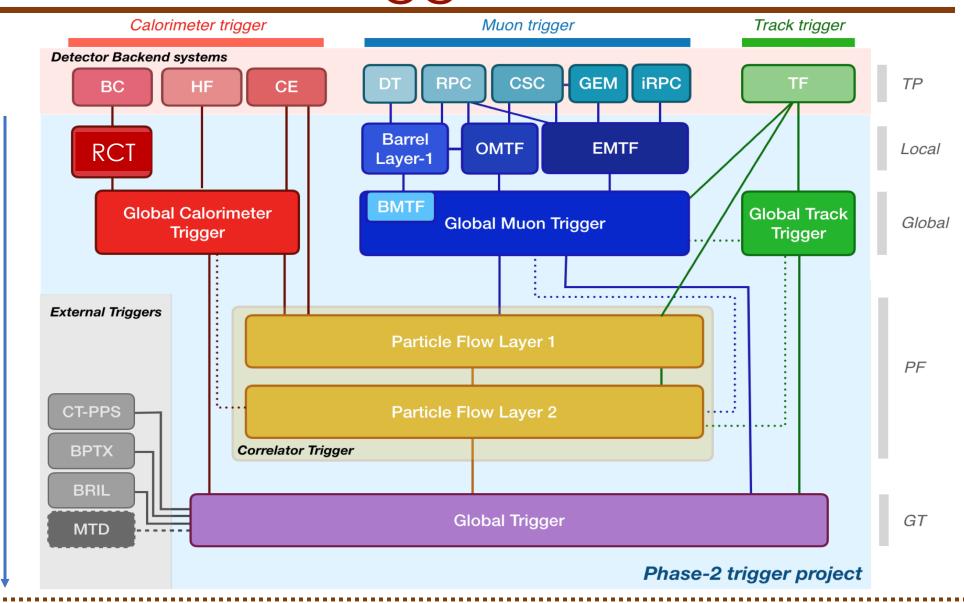

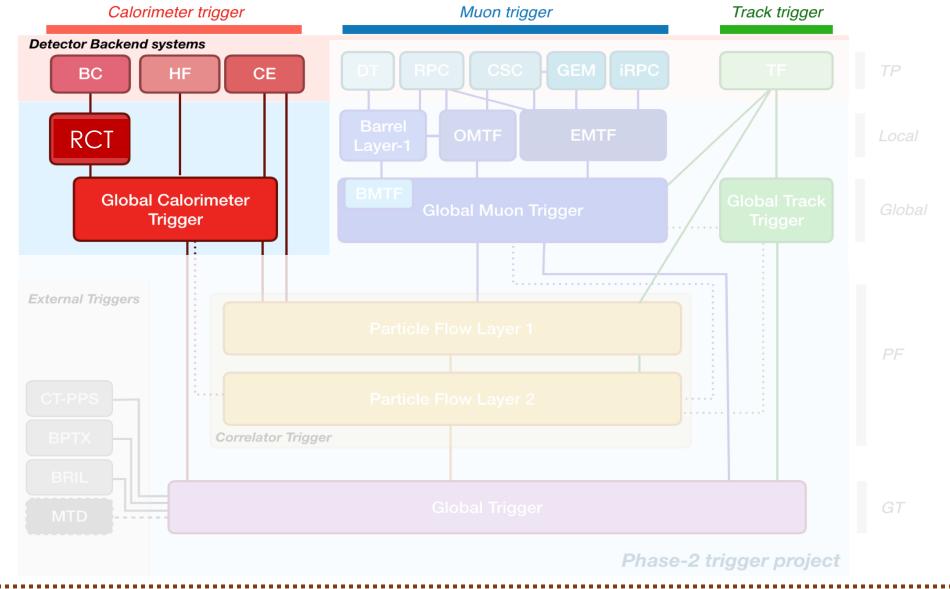

#### Phase-2 Level-1 Trigger

#### Phase-2 Calorimeter Level-1 Trigger

#### **INPUTS:**

- ECAL crystals

- HCAL towers

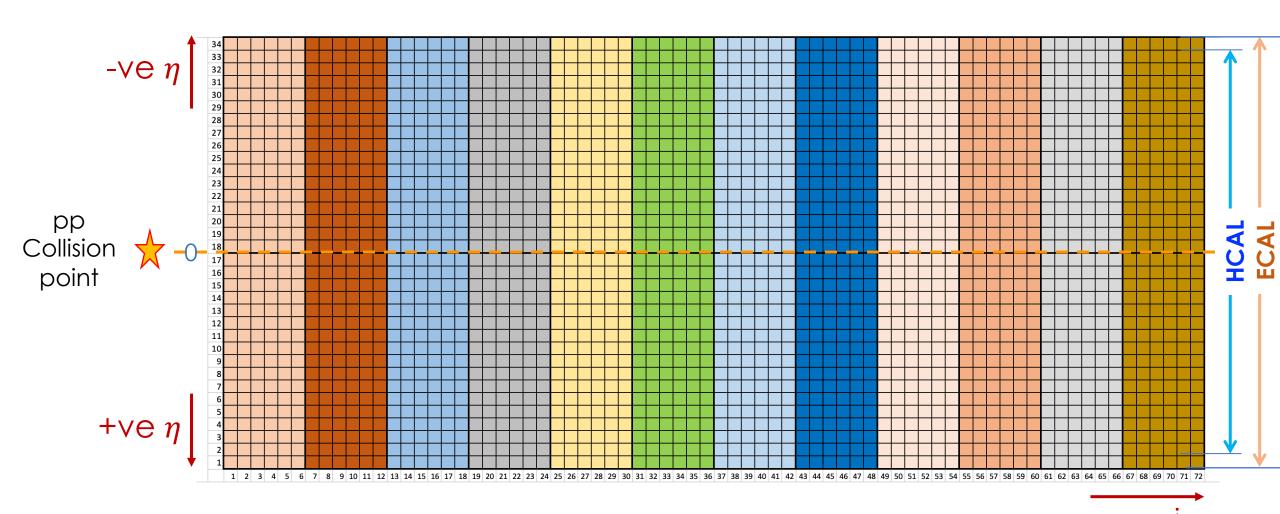

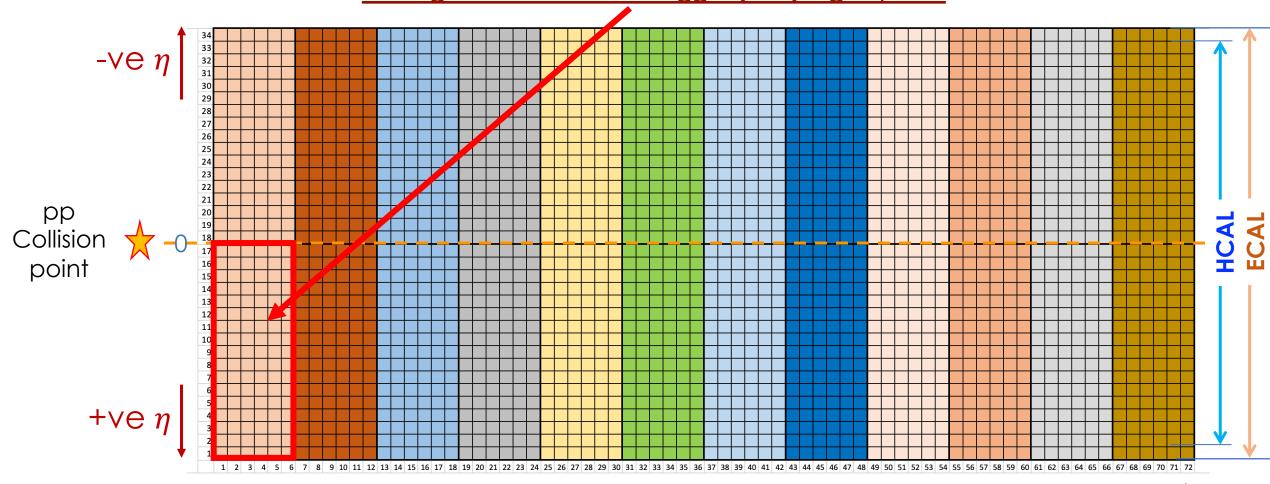

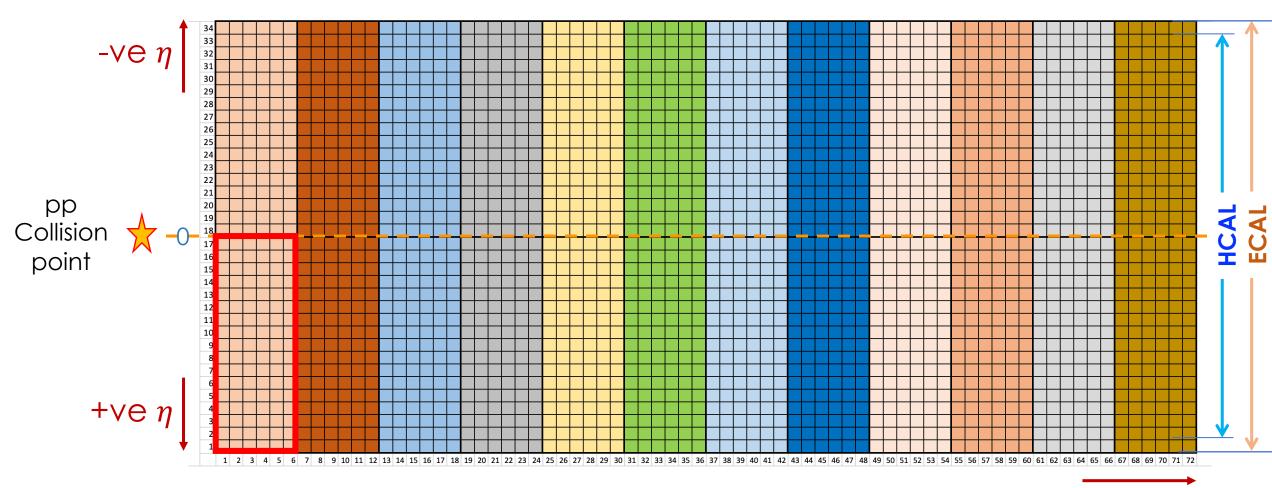

### Barrel Calorimeter Segmentation

### Barrel Calorimeter Segmentation

### Barrel Calorimeter Segmentation

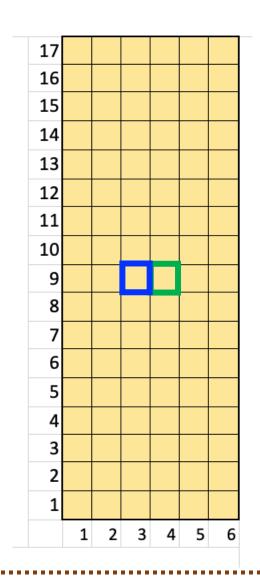

Full barrel Calorimeter: 24 RCT regions/cards

## Project: Write & Synthesis an algorithm for single re-designed RCT

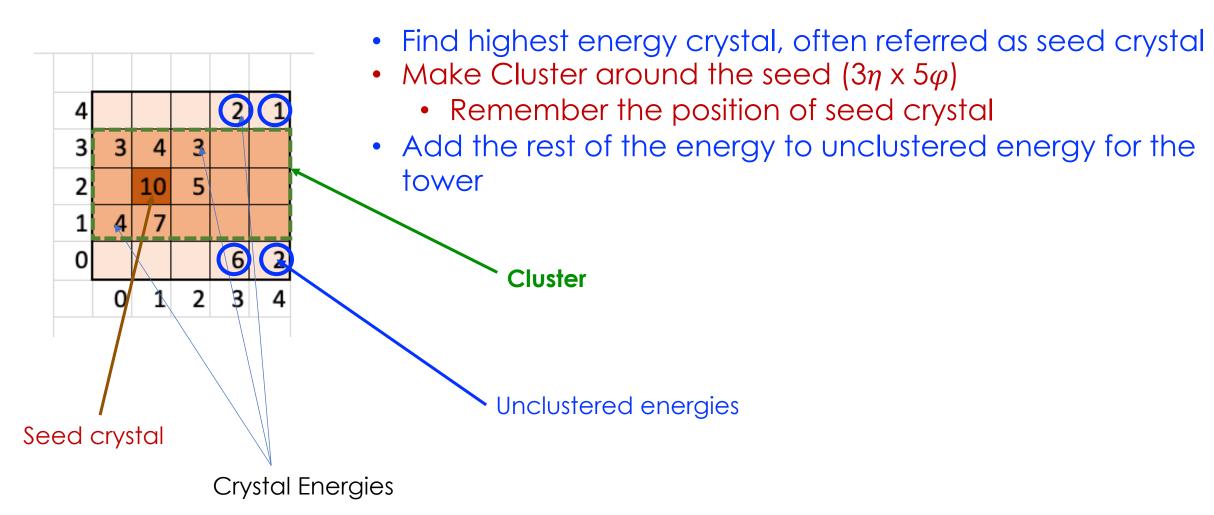

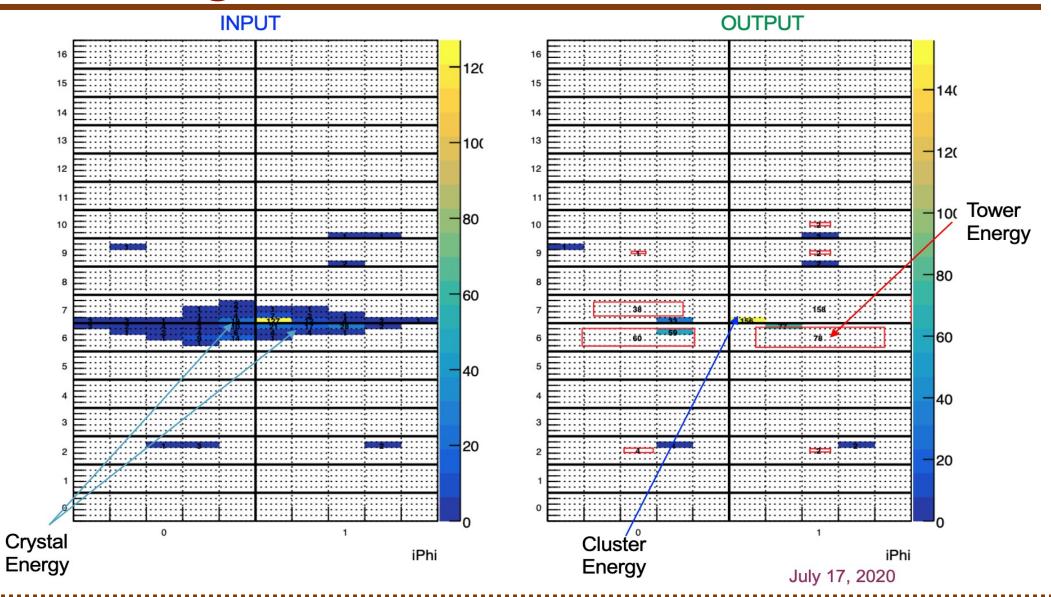

#### RCT Algorithm

- Take energy input from Calorimeter

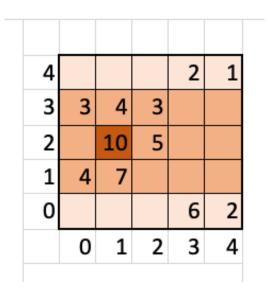

- Cluster ECAL energy for each tower

- Keep the position (eta, phi) of the seed (highest energetic) crystal

- Add HCAL tower energy to clustered tower

- Keep unclustered for respective tower

- Stitch clusters on boundary

- Sort highest 12 clusters and send as output

- Cluster ET

- Position of towers and corresponding seed crystal within tower

- Unclustered Energy

### Single RCT

#### Physics bandwidth vs Algo Clock @ 25G

| LHC BC Clock [MHz]       | 40.08    |

|--------------------------|----------|

| Word Bit Size            | 66       |

| Line Rate [Gbps]         | 25.78125 |

| Max Theoretical Words/Bx | 9.74613  |

| Bx Frame Length (TM interval) | 1       | 1       | 1       |

|-------------------------------|---------|---------|---------|

| Words/Frame                   | 7       | 8       | 9       |

| Equiv. Words/Bx               | 7.00    | 8.00    | 9.00    |

| Equiv. Bits/Bx                | 448     | 512     | 576     |

| Data Rate [Gbps]              | 18.52   | 21.16   | 23.81   |

| Filler Rate [Gbps]            | 7.26    | 4.62    | 1.97    |

| Average Filler Words/Bx       | 2.75    | 1.75    | 0.75    |

| Average Filler Words/Orbit    | 9787.22 | 6223.22 | 2659.22 |

| Average Filler Words/Frame    | 2.75    | 1.75    | 0.75    |

| Payload Bits/Frame            | 448     | 512     | 576     |

| Algo Clock @ 64b i/f[MHz]     | 280.56  | 320.64  | 360.72  |

#### Algorithm

#### 1. Input per tower

- ECAL: 25 crystal energies

- Each crystal 16b, total: 400b

- HCAL: tower energy

- Each tower: 16b

| 1 - ECAL crystals = 16b | 10 ET + 5 timing + 1 Spike |

|-------------------------|----------------------------|

| 1 - HCAL towers = 16b   | 10 ET + 6 feature bits     |

- Total input: 416b (ECAL + HCAL)

- 1 link can have 576 bits

- Lets assume 1 link carries 1 tower worth of information (416 b)

- We need total of 102 input links

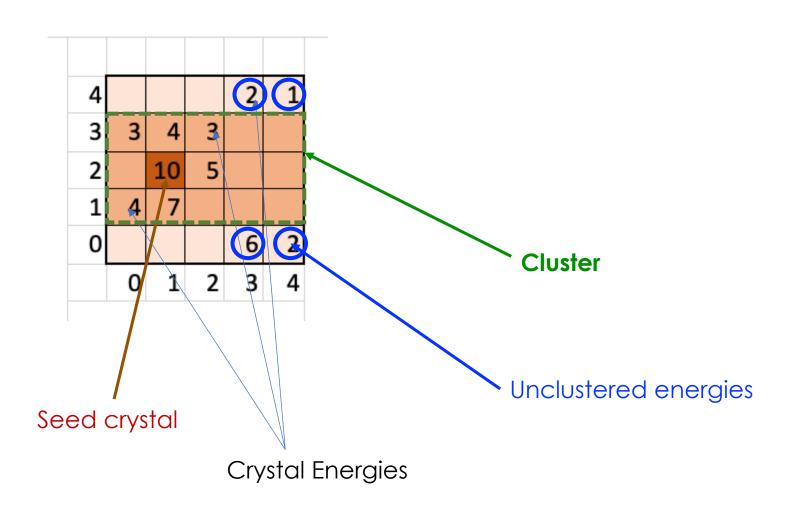

#### 2. Cluster these energies

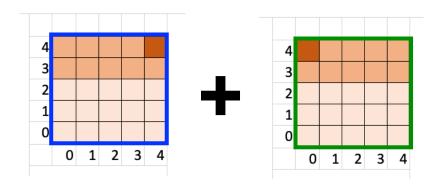

#### Clustering energies in ECAL

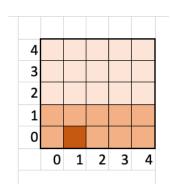

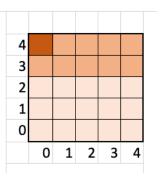

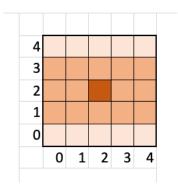

$2\eta \times 5\varphi$  cEta:4, cPhi:4

$2\eta \times 5\varphi$  cEta:0, cPhi:1

$2\eta \times 5\varphi$  cEta:4, cPhi:0

$3\eta \times 5\varphi$  cEta:2, cPhi:2

#### Algorithm

#### 1. Input per tower

- ECAL: 25 crystal energies

- Each crystal 16b, total: 400b

- HCAL: tower energy

- Each tower: 16b

| 1 - ECAL crystals = 16b | 10 ET + 5 timing + 1 Spike |

|-------------------------|----------------------------|

| 1 - HCAL towers = 16b   | 10 ET + 6 feature bits     |

- Total input: 416b (ECAL + HCAL)

- 1 link can have 576 bits

- Lets assume 1 link carries 1 tower worth of information (416 b)

- We need total of 102 input links

#### 2. Cluster these energies

Make clusters for each of these towers

#### Algorithm

- 1. Input per tower

- 2. Cluster ECAL energies for each tower

- Divide the RCT card further to make life simple

#### Divide & Rule

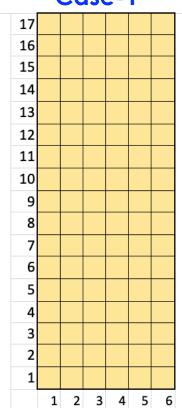

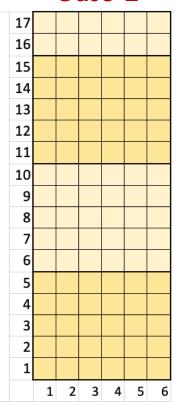

Case-1

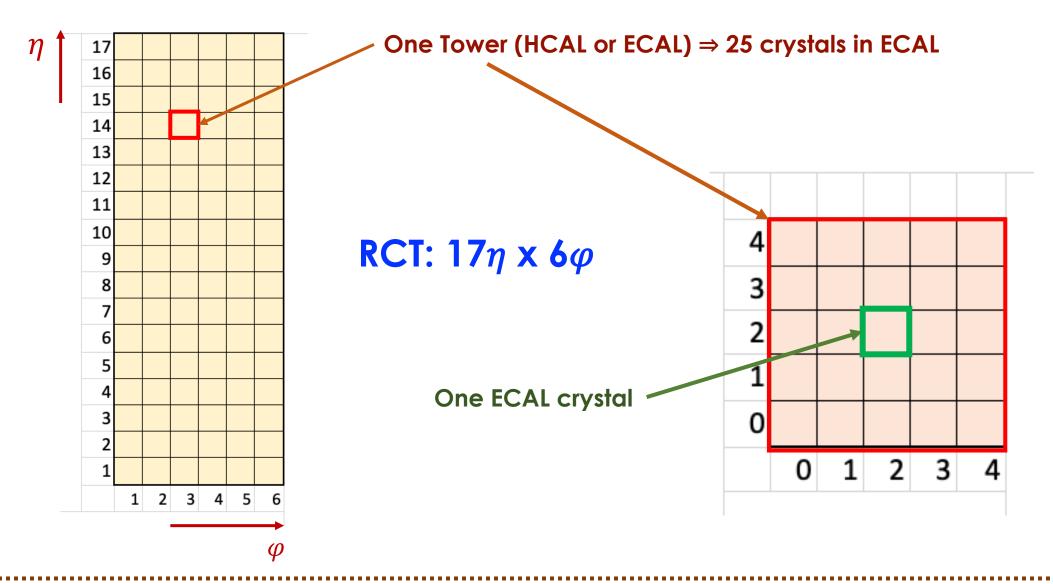

1 RCT region:  $17\eta \times 6\varphi$

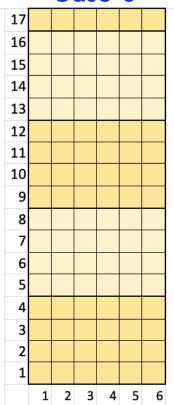

Case-2

1 RCT region:  $17\eta \times 6\varphi$

- 4 sub-regions:

- 3:  $5\eta \times 6\varphi + 1$ :  $2\eta \times 6\varphi$

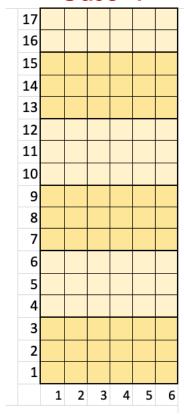

Case-3

1 RCT region:  $17\eta \times 6\varphi$

- 5 sub-regions:

- 4:  $4\eta \times 6\varphi + 1$ :  $1\eta \times 6\varphi$

#### Case-4

1 RCT region:  $17\eta \times 6\varphi$

- 6 sub-regions:

- 5:  $3\eta \times 6\varphi + 1$ :  $2\eta \times 6\varphi$

#### Choose wisely

- Case-1

- 102 cluster

- Case-2

- 30 or 12 cluster per sub-region

- Case-3

- 24 or 6 cluster per sub-region

- Case-4

- 18 or 12 cluster per sub-region

#### Algorithm

- 1. Input per tower

- 2. Cluster ECAL energies for each tower

- Divide the RCT card further to make life simple

- 3. Stitch together the clusters for neighbouring towers and add HCAL energies for respective towers

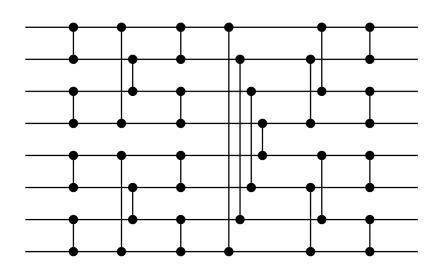

### Stitching

Add energies if seed crystal are neighbor for neighboring towers

#### Choose wisely

- Case-1

- 102 cluster

- Send 12 output tower

- Case-2

- 30 or 12 cluster per sub-region

- Send out 7 towers per sub-region (28 total towers)

- Case-3

- 24 or 6 cluster per sub-region

- Send out 6 towers per sub-region (30 total towers)

- Case-4

- 18 or 12 cluster per sub-region

- Send out 5 towers per sub-region (30 total towers)

#### Algorithm

- 1. Input per tower

- 2. Cluster ECAL energies for each tower

- Divide the RCT card further to make life simple

- 3. Stitch together the clusters for neighbouring towers

- 4. Sort the final list of towers

## Sorting

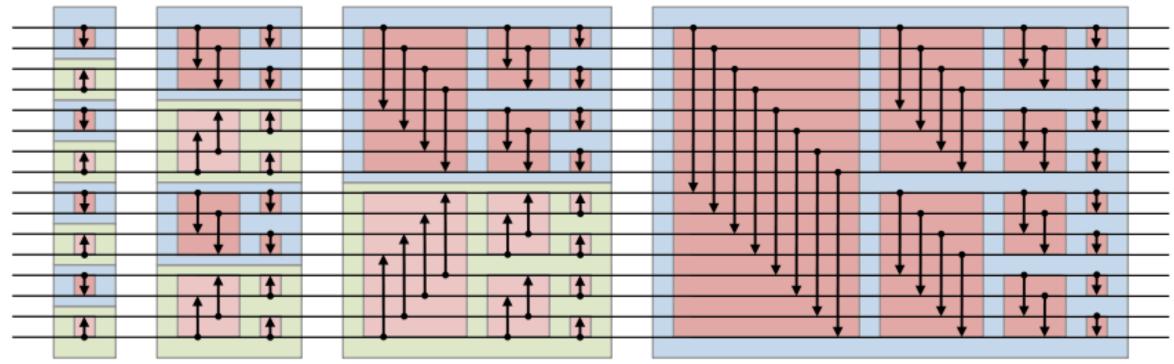

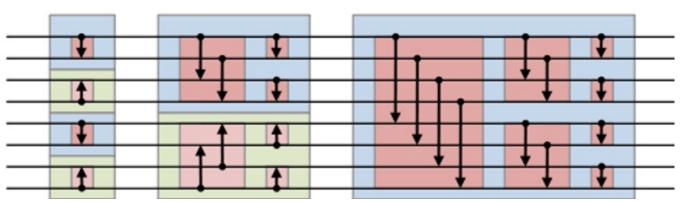

#### Bitonic Sorter

- Comparison-based sorting algorithm that can run in parallel

- Converts random sequence of numbers into a bitonic sequence

- One that monotonically increases, then decreases

Fig: Bitonic sort with 16 elements

#### Algorithm

- o Inputs: random set of  $2n = 2^k$  (k is +ve integer) numbers

- Every pair of elements is bitonic

- Bitonic sequences of size-2 are merged to create ordered lists of size 2

- At the end of this stage of merging, we have N/4 bitonic sequence of size 4

- o Bitonic sequence of size-4 are merged into sorted sequence of size 4, leading to N/8 bitonic sequence of size 8 and so on...

- $\circ$  Given an unordered sequence of 2n, we have  $log_2 2n$  stages

#### Bitonic Sorter

OBitonic sort is a classic parallel algorithm for sorting & thus for FPGAs

$\circ$  No. of comparisons:  $O(n\log^2(n))$

- OSuitable for hardware implementation:

- Parallel implementation

- Compare elements in a predefined sequence & doesn't depend on data

- Only be done for elements: 2<sup>n</sup>

#### An example

| 3 | 3 |          | 3   | 2 |          | 2   | 2 | 2 |

|---|---|----------|-----|---|----------|-----|---|---|

| 9 | 9 |          | 2   | 3 |          | 3   | 3 | 3 |

| 2 | 7 |          | 7   | 7 |          | 5   | 5 | 4 |

| 7 | 2 | +        | 9 * | 9 |          | 4   | 4 | 5 |

| 5 | 5 | <b>+</b> | 8   | 8 | <b>+</b> | 8   | 7 | 6 |

| 6 | 6 | <b>↑</b> | 6   | 6 | +        | 6   | 6 | 7 |

| 4 | 8 |          | 5   | 5 | 1        | 7 + | 8 | 8 |

| 8 | 4 |          | 4   | 4 | <b>+</b> | 9   | 9 | 9 |

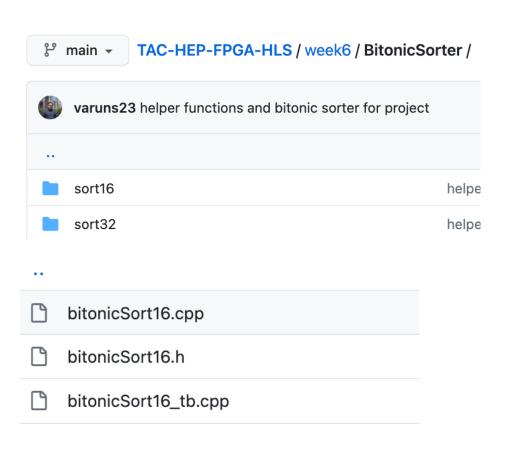

#### Ready to use code

#### https://github.com/varuns23/TAC-HEP-FPGA-HLS/tree/main/week6/BitonicSorter

```

1 #include "bitonicSort16.h"

//Main CAE block (compare and exchange)

GreaterSmaller AscendDescend(const din_t &x, const din_t &y){

#pragma HLS PIPELINE II=9

#pragma HLS INLINE

GreaterSmaller s;

s.greater = (x > y) ? x : y;

10

s.smaller = (x > y) ? y : x;

11

12

return s;

13

14

void FourinSmallFir(const din_t &x0, const din_t &x1, const din_t &x2, const din_t &x3,

16

din t &y0, din t &y1, din t &y2, din t &y3){

17

#pragma HLS PIPELINE II=9

18

#pragma HLS INLINE

19

GreaterSmaller res;

20

res = AscendDescend(x0, x2);

21

y0 = res.smaller; y2 = res.greater;

22

23

res = AscendDescend(x1, x3);

24

y1 = res.smaller; y3 = res.greater;

25

26

void FourinGreatFir(const din_t &x0, const din_t &x1, const din_t &x2, const din_t &x3,

28

din_t &y0, din_t &y1, din_t &y2, din_t &y3){

29

#pragma HLS PIPELINE II=9

30

#pragma HLS INLINE

31

GreaterSmaller res;

32

res = AscendDescend(x0, x2);

33

y0 = res.greater; y2 = res.smaller;

34

35

res = AscendDescend(x1, x3);

36

y1 = res.greater; y3 = res.smaller;

37

https://github.com/varuns23/TAC-HEP-FPGA-HLS/blob/main/week6/BitonicSorter/sort16/bitonicSort16.cpp

```

#### Algorithm

- 1. Input per tower

- 2. Cluster ECAL energies for each tower

- Divide the RCT card further to make life simple

- 3. Stitch together the clusters for neighbouring towers

- 4. Sort the final list

- 5. Send just 12 towers per RCT region

#### Output

- 12 towers

- Information per tower

- Clustered energy (32b)

- Unclustered energy (32b)

- Seed crystal position (cEta, cPhi)

- Tower position (tEta, tPhi)

- HoE (Ratio of HCAL/ECAL energies)

#### Contrainsts to use

- Target Clock Period

- 2.7778ns

- Uncertainty

- 30%

- Target Device

- xcvu9p-flgc2104-1-e

#### Some functions to refer from

https://github.com/varuns23/TAC-HEP-FPGA-HLS/tree/main/week6

```

17

uint16_t getPeakBinOf5(uint16_t et[NCrystalsPerEtaPhi], uint16_t etSum);

18

bool getClustersInTower(uint16_t crystals[NCrystalsPerEtaPhi] [NCrystalsPerEtaPhi],

19

20

uint16_t *peakEta,

21

uint16_t *peakPhi,

22

uint16_t *largeClusterET,

23

uint16_t *smallClusterET);

24

bool mergeClusters(uint16_t ieta1, uint16_t iphi1, uint16_t itet1, uint16_t icet1,

26

uint16_t ieta2, uint16_t iphi2, uint16_t itet2, uint16_t icet2,

27

uint16_t *eta1, uint16_t *phi1, uint16_t *tet1, uint16_t *cet1,

uint16_t *eta2, uint16_t *phi2, uint16_t *tet2, uint16_t *cet2);

28

29

void stitchNeighbors(bool stitch, Tower Ai, Tower Bi, Tower &Ao, Tower &B);

```

algo\_top.cppalgo\_top.hhelperFunctions.cpphelperFunctions.h

#### Summary: Project

## Write an algorithm to cluster ECAL and HCAL energies for Regional Calorimeter Trigger using HLS and synthesis the results

- 1. Input per tower (ECAL + HCAL)

- 2. Cluster ECAL energies for each tower

- Divide the RCT card further to make life simple

- 3. Stitch together the clusters for neighbouring towers

- 4. Sort the final list

- 5. Send just 12 towers per RCT region

## Questions?

## Acknowledgement

Lectures are compiled using content from Xilinx's public pages/examples or different user guides

## Additional material

### Assignment submission

- Where to submit:

- https://pages.hep.wisc.edu/~varuns/assignments/TAC-HEP/

- Use your login machine credentials

- Submit one file per week

- Try to submit by following week's Tuesday

#### Correct Time

#### From 03.28.2023 onwards

- Tuesdays: 9:00-10:00 CT / 10:00-11:00 ET / 16:00-17:00 CET

- Wednesday: 11:00-12:00 CT / 12:00-13:00 ET / 18:00-19:00 CET

#### Jargons

- ICs Integrated chip: assembly of hundreds of millions of transistors on a minor chip

- PCB: Printed Circuit Board

- LUT Look Up Table aka 'logic' generic functions on small bitwidth inputs. Combine many to build the algorithm

- FF Flip Flops control the flow of data with the clock pulse. Used to build the pipeline and achieve high throughput

- DSP Digital Signal Processor performs multiplication and other arithmetic in the FPGA

- BRAM Block RAM hardened RAM resource. More efficient memories than using LUTs for more than a few elements

- PCIe or PCI-E Peripheral Component Interconnect Express: is a serial expansion bus standard for connecting a computer to one or more peripheral devices

- **InfiniBand** is a computer networking communications standard used in high-performance computing that features very high throughput and very low latency

- **HLS** High Level Synthesis compiler for C, C++, SystemC into FPGA IP cores

- DRCs Design Rule Checks

- **HDL** Hardware Description Language low level language for describing circuits

- RTL Register Transfer Level the very low level description of the function and connection of logic gates

- **FIFO** First In First Out memory

- Latency time between starting processing and receiving the result

- Measured in clock cycles or seconds

- II Initiation Interval time from accepting first input to accepting next input

#### Assignment Week-3

- Use target device: xc7k160ffbg484-2

- Clock period of 10ns

- 1. Execute the code (lec5Ex2.tcl) using CLI (slide-25) and compare the results with GUI results for C-Simulation, C-Synthesis

- 2. Vary following parameters for two cases: high and very high values and compare with 1 for both CLI and GUI

- Variable: "samples"

- · Variable: "N"

- 3. Run example lec3Ex2a

#### Assignment Week-4

- 1. Do a matrix multiplication of two 1-dimensional arrays A[N]\*B[N], where N > 5

- a) Report synthesis results without any pragma directives

- b) Add as many pragma directives possible

- i. Report any conflicts (if reported in logs) between two pragmas

- 2. Compare the analysis perspective (Performance) for different case shared today

- 3. For Array\_partitioning, instead of using complete, use block and cyclic with different factors

#### Assignment Week-5

- 1. Do exercise mention on slide-24

- 2. A matrix multiplication using two for loops and compare results for pragma loop\_flatten & unroll

- 3. Write a simple program doing arithmetic operations(+, -, \*, /, %) between two variable use of arbitrary precision to compare results between stand c/c++ data types and using ap\_(u)int<N>

- 4. Write a program using an array with N(=10/15/20) elements and then restructure the code with a struct having N-data member. Compare the results of two programs